Challenge is a HORIZON 2020 project financed under the NMBP (Nanotechnologies, advanced Materials, Biotechnology and Production) work programme that studies growth, processing and devices in cubic silicon carbide (3C-SiC).

3C-SiC technology can have a large impact on the future power device market and is particularly suited for implementation in hybrid electrical vehicles

Silicon carbide presents a high breakdown field (2-4 MV/cm) and a high energy band gap (2.3–3.2 eV), largely higher than for silicon. Within this frame, the cubic polytype of SiC (3C-SiC) is the only one that can be grown on a host substrate with the huge opportunity to grow only the silicon carbide thickness required for the targeted application. The possible growth on silicon substrate has remained for long period a real advantage in terms of scalability regarding the reduced diameter of hexagonal SiC wafer commercially available. Even the relatively narrow band-gap of 3C-SiC (2.3eV), which is often regarded as detrimental in comparison with other polytypes, can in fact be an advantage. The lowering of the conduction band minimum brings about a reduced density of states at the SiO2/3C-SiC interface and MOSFET on 3C-SiC has demonstrated the highest channel mobility of above 300 cm2/(Vxs) ever achieved on SiC crystals, prompting a remarkable reduction in the power consumption of these power switching devices.

The electrical activity of extended defects in 3C SiC is a major concern for electronic device functioning. To achieve viable commercial yields the mechanisms of defects must be understood and methods for their reduction developed..

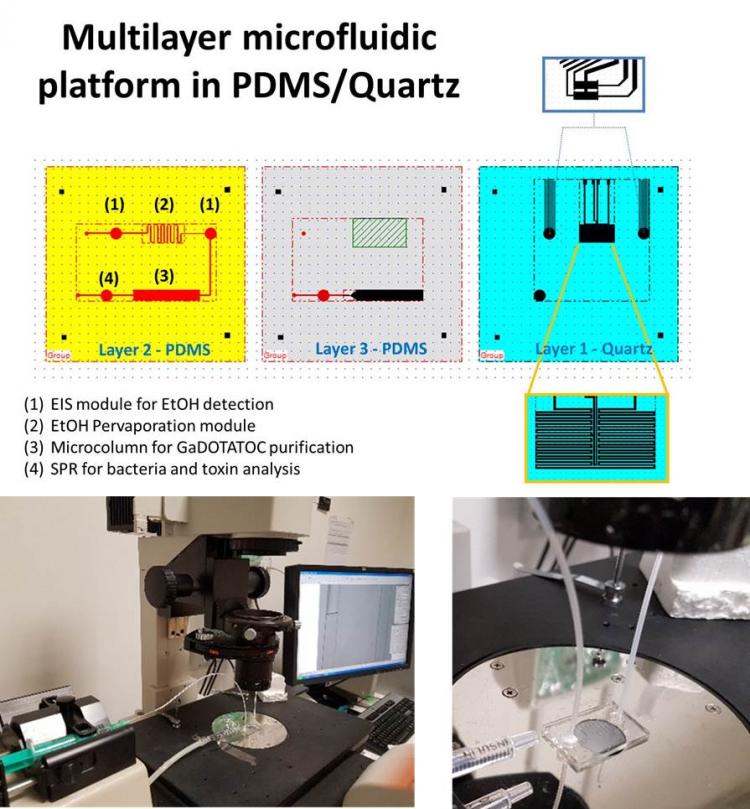

In this project new approaches for the reduction of defects will be used, working on new compliance substrates that can help to reduce the stress and the defect density at the same time. This growth process will be driven by numerical simulations of the growth and simulations of the stress reduction.

The structure of the final devices will be simulated using the appropriated numerical tools where new numerical model will be introduced to take into account the properties of the new material. Thanks to these simulations tools and the new material with low defect density, several devices that can work at high power and with low power consumption will be realized in this project.

CHALLENGE is a Horizon 2020 project aiming to find an economical solution in response to the needs of a very critical section of the power market; proposing new devices for improving power efficiency in the consumer market between 600V and 1200V. Therefore the 4 year project intends to solve this problem and facilitate the use of a cost effective, low environmental impact new material in the semiconductor family.

Partners are coming from the most advanced public research centres and highly respected Universities on SiC technologies in Europe. The research portfolio ranges from large companies - world leaders in the field and many SMEs from 6 different EU countries in addition to Japan. They will propose a toolbox of solutions for the reduction of defects in bulk cubic silicon carbide material based around new compliance substrates with the ability to develop strategic applications in several fields: from telecommunication to automotive, from consumer electronics to electrical household appliances, from industrial applications to home automation.

The Challenge consortium is unique in breadth across the whole supply chain (equipment, materials, characterizations, processing, power devices, simulations). With the consortiums promise to collect high level research and innovation together with impressive partners’ profiles, this ambitious project can only be brought together with the great support of an EU project.

The project is coordinated by CNR-IMM.

Project coordinator: Francesco La Via